Zynq UltraScale MPSoC Base TRD 2018.1 - Design Module 1

Zynq UltraScale MPSoC Base TRD 2018.1 - Design Module 1

Table of Contents

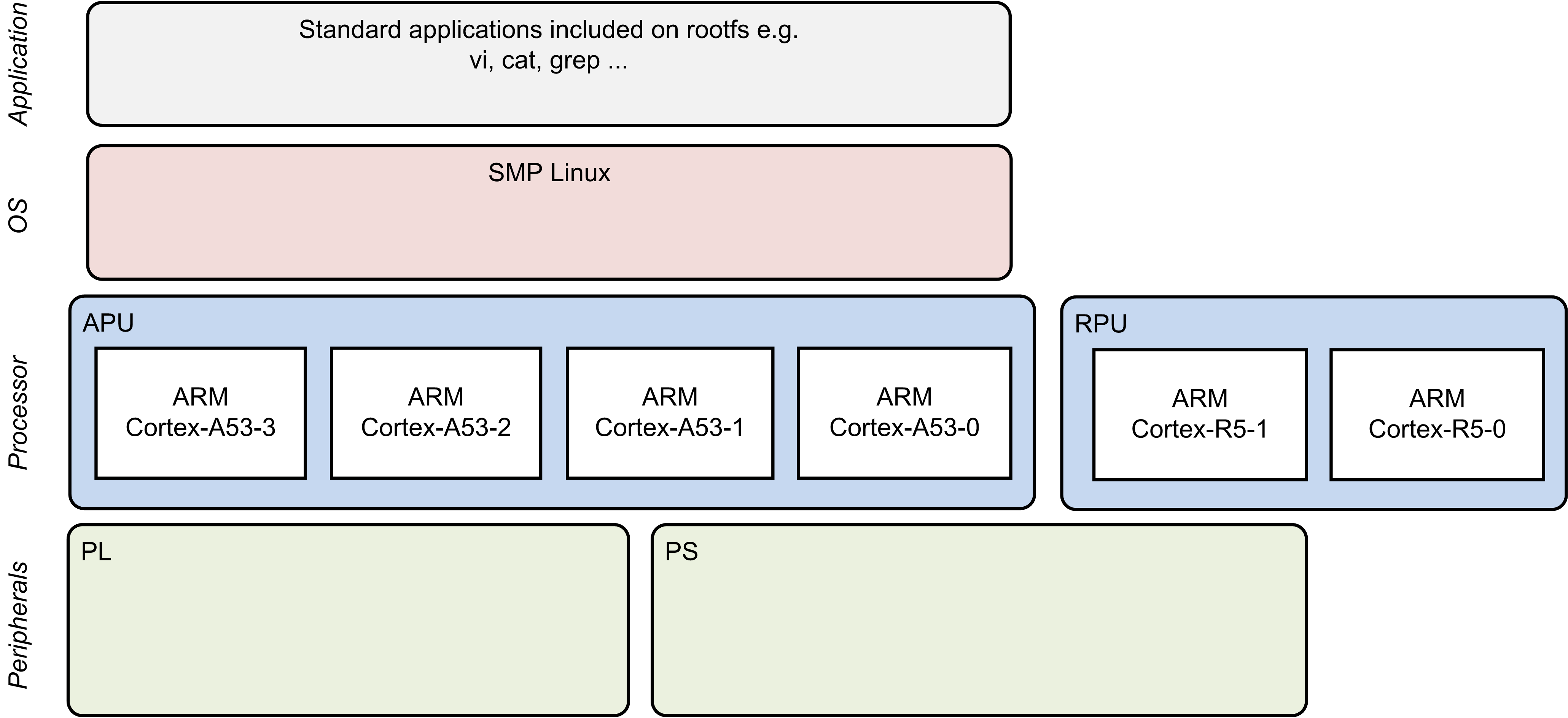

Design Overview

This design module showcases the following:

- Boot APU only

- FSBL, ATF, U-boot, PMU-FW

- APU OS: SMP Linux

- Ethernet via FTP/SCP

- Serial console via UART0

- File system via SD, USB or SATA

- Standard Linux applications on rootfs

Design Components

- petalinux_bsp

- zynqmp_fsbl

- pmufw

- bl31

- u-boot

- kernel

- device tree (zcu102-base-dm1.dtsi)

- rootfs

Build Flow Tutorials

Petalinux BSP

This tutorial shows how to build the Linux image and boot image using the PetaLinux build tool.

- Configure the PetaLinux project.

% cd $TRD_HOME/petalinux % petalinux-create -t project -s zcu102-base-trd.bsp -n bsp % cd bsp % petalinux-config --get-hw-description=$TRD_HOME/zcu102_base_trd/sw/a53_linux/a53_linux/prebuilt --oldconfig

Note: This step will result in a warning message that can be safely ignored (AR#71172)

WARNING: Usage of HDF is going to be deprecated in future releases.Please use DSA(Device Support Archive) instead.

- Select the device-tree matching design module 1 and build all Linux image components

% cd $TRD_HOME/petalinux/bsp/project-spec/meta-user/recipes-bsp/device-tree/files/ % cp zcu102-base-dm1.dtsi system-user.dtsi % petalinux-build

- Create a boot image.

% cd $TRD_HOME/petalinux/bsp/images/linux % petalinux-package --boot --bif=../../project-spec/boot/dm1.bif --force

- Copy the generated boot image and Linux image to the dm1 SD card directory.

% mkdir -p $TRD_HOME/sd_card/dm1 % cp BOOT.BIN image.ub $TRD_HOME/sd_card/dm1

Run Flow Tutorial

- See here for board setup instructions.

- Copy all the files from the $TRD_HOME/sd_card/dm1 SD card directory to a FAT formatted SD card.

- Power on the board to boot the images; make sure all power rail LEDs are lit green.

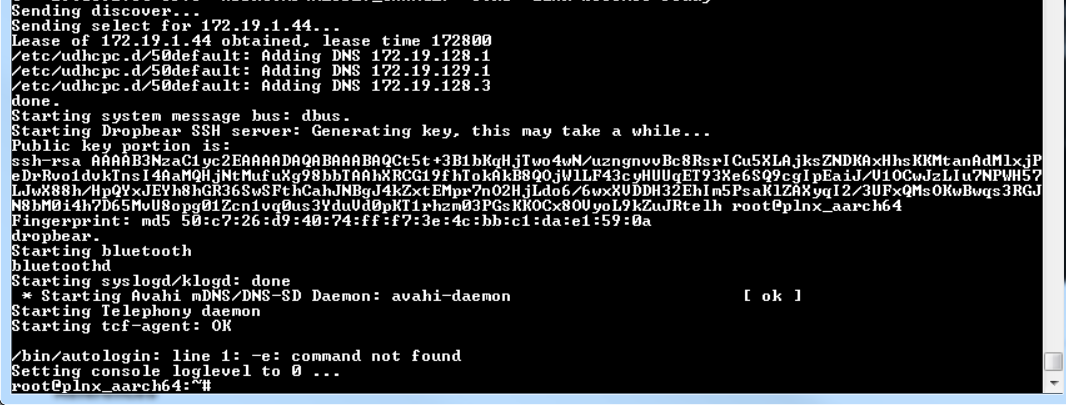

- The user can now see Linux boot on the serial console:

References

- How to mount a USB3 or SATA hard drive:

http://www.wiki.xilinx.com/SATA

http://www.wiki.xilinx.com/Zynq+Ultrascale+MPSOC+Linux+USB+device+driver (under host mode)

Continue with Design Module 2.

Return to the Design Tutorials Overview.

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy