ZU+ Example - PM Hello World

Table of Contents

Note: This page is for Xilinx SDK up to v2019.1 only. For 2019.2 onward please refer ZU+ Example - PM Hello World (for Vitis 2019.2 onward).

Prerequisites

- You have a ZCU102 development board.

- You have used the SDK to build.

PM Hello World

This is an empty application that does PM initialization and prints "Hello World!" to the UART. Please use this as a starting point for creating new PM applications for other design examples provided here.Steps to create and build this example

- Download these source files.

For SDK 2017.4 and older version: hello_source_2017_4.zip

For SDK 2018.1 and newer version: hello_source_2017_4.zip - Extract the zip file. The source directory contains application main.c file and other required files.

- Start Xilinx SDK 2017.1.

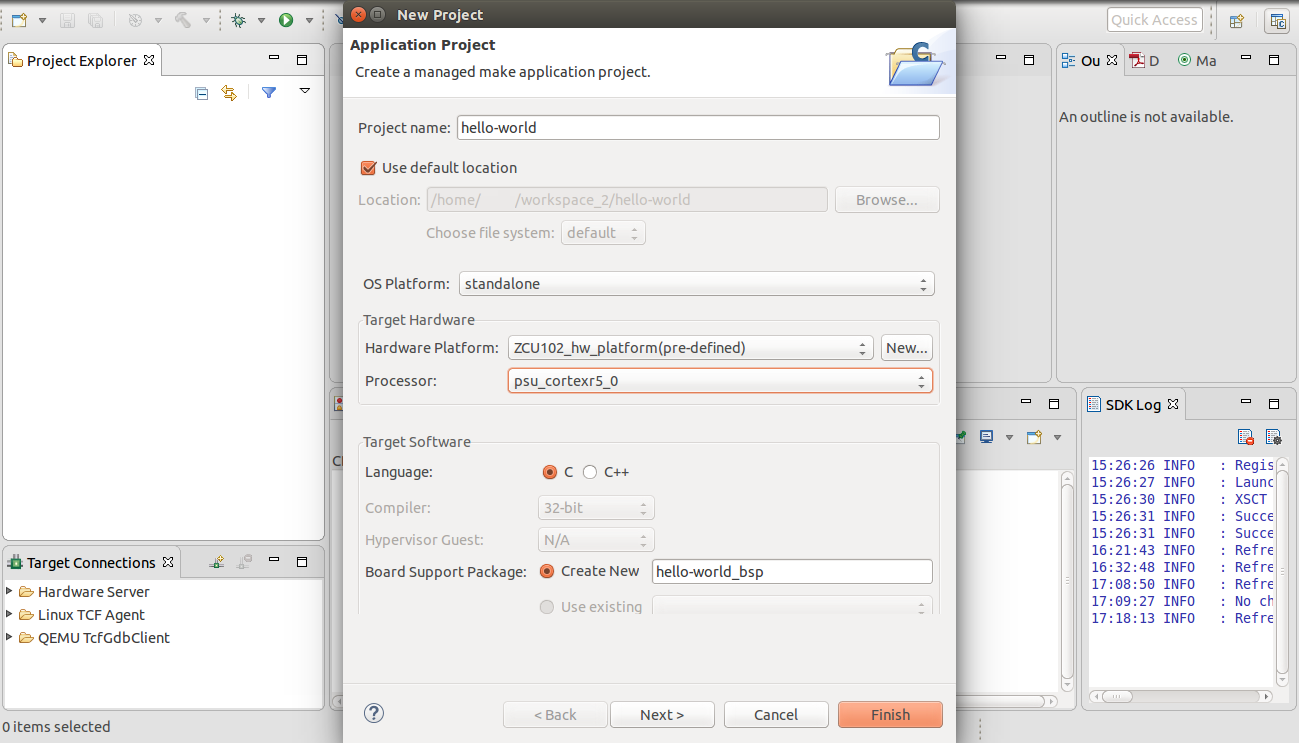

- Go to File → New → Application Project.

- Give a project name Ex. Hello-world.

- Select standalone in OS Platform category. Select ZCU102_hw_platform in Hardware Platform category. Select appropriate processor (e.g. psu_cortextr5_0) from the processor list. Then select next.

- Select empty application from the template then select finish to create project. Wait for the BSP to complete building before proceeding.

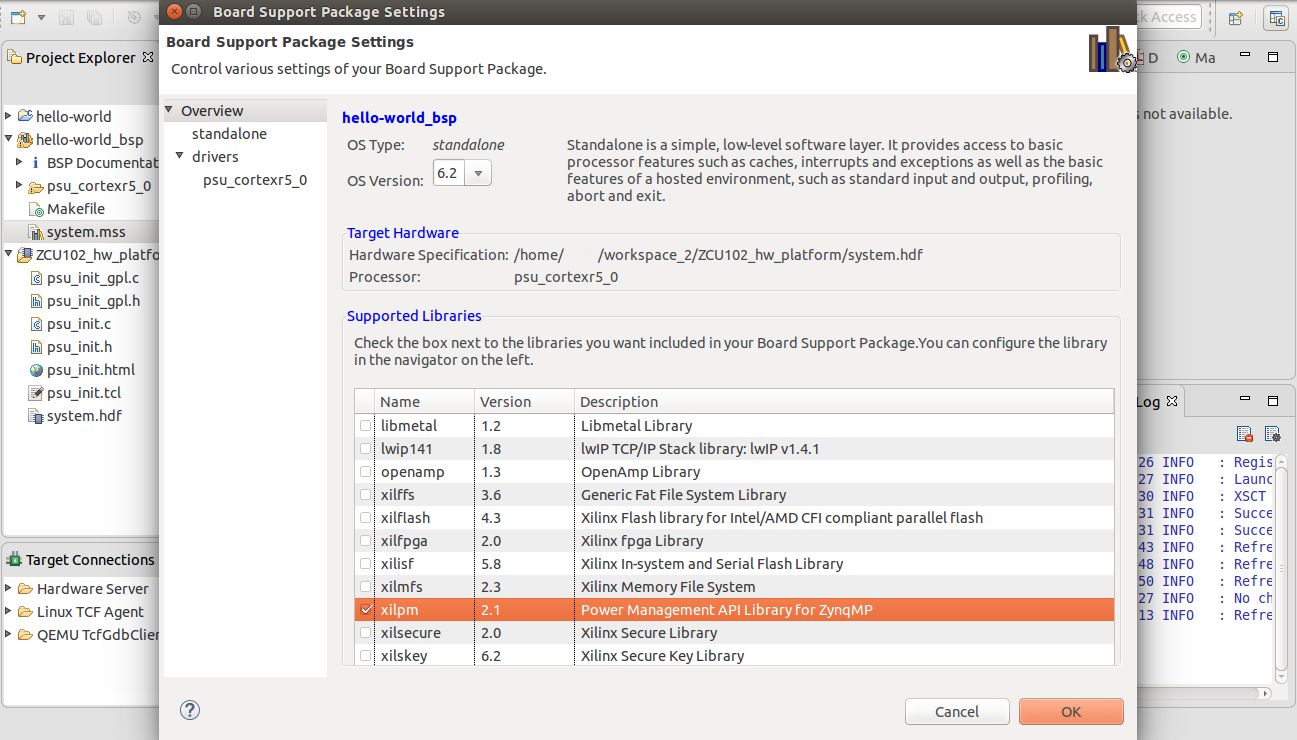

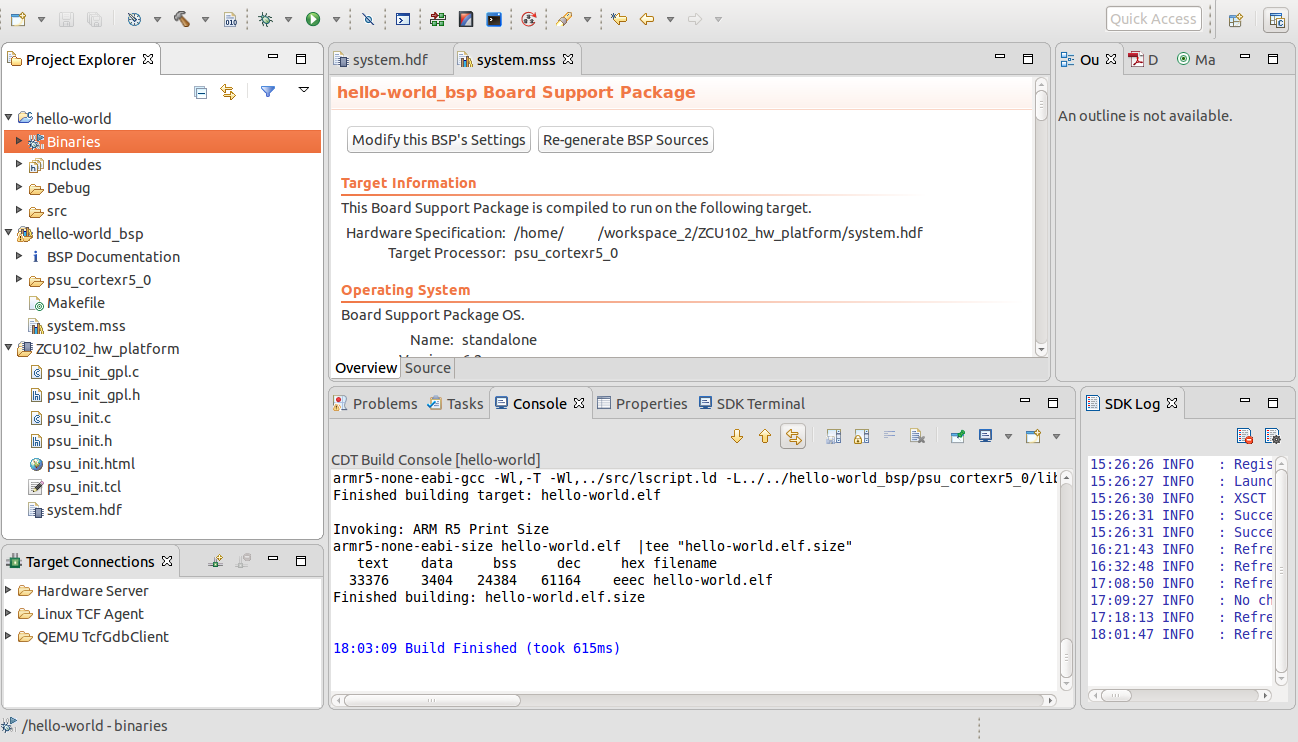

- Now from system.mss file click on “Modify this BSP's Settings”. Select xilpm library from Board Support Package Settings dialog box and click OK. Re-generate BSP Sources.

- Now right click on hello-world from Project Explorer window, select Properties from drop-down menu and go to Resource. A location of the project will be displayed.

- Go to that location, a folder named “src” will be present. Copy all the files extracted from source.zip file into src folder. Refresh the project by right clicking on hello-world from Project Explorer and selecting refresh option.

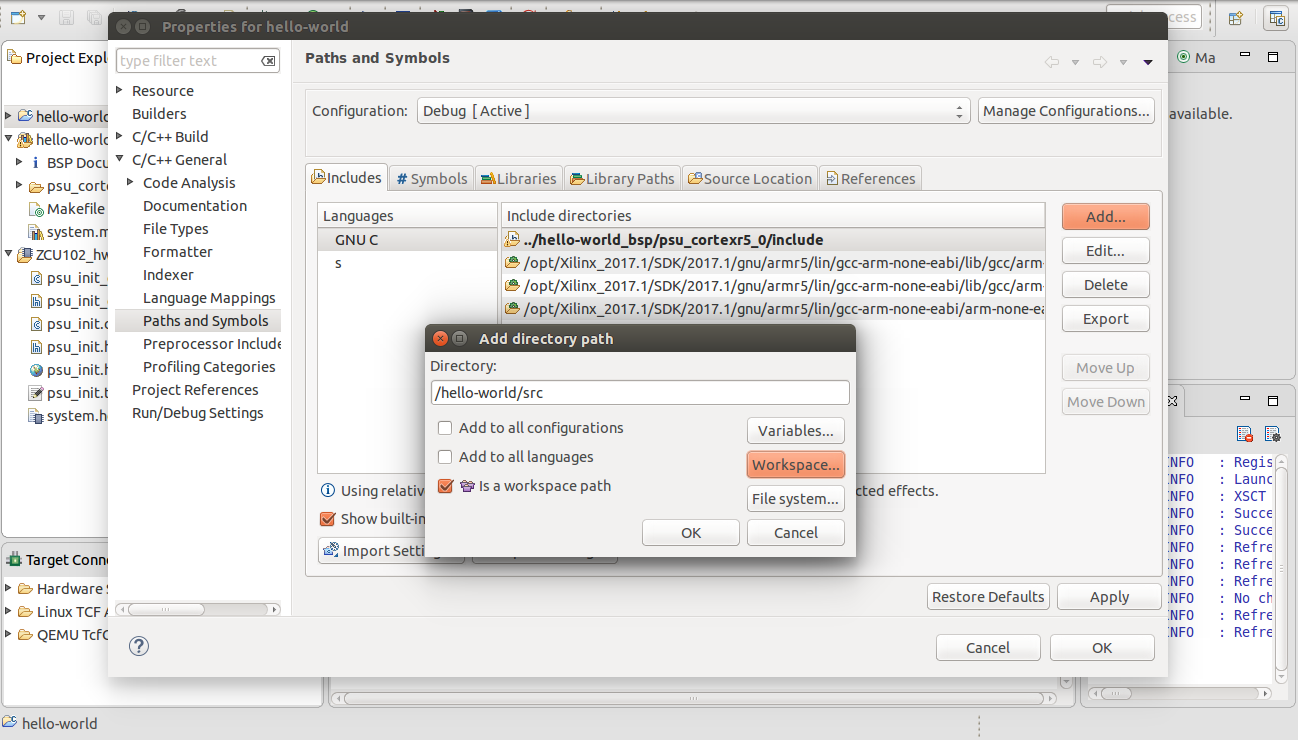

- From the Project Explorer window, right click on hello-world, select Properties, expand C/C++ General, and go to Paths and Symbols.

- Add ../hello-world/src path in includes section. Click OK.

- Hello-world example will be build automatically.

Configuration Object

Configuration Object file Generated by PetaLinux tool chain and Vivado is attached below.pm_cfg_obj.c

Note: Add this file in the src folder of the application in order to use configuration object.

Subsystems -

1) Linux Subsystem

Master -

- APU

- DDR

- L2 Cache

- OCM Bank 0, 1, 2 and 3

- I2C0

- I2C1

- SD1

- QSPI

- PL

2) R5-0 Subsystem

Master -

- RPU0

- TCM Bank 0 - A

- TCM Bank 0 - B

3) R5-1 Subsystem

Master -

- RPU1

- TCM Bank 1 - A

- TCM Bank 1 - B

RPU to run from TCM

By default, RPU applications are compiled to run from the DDR memory. In many cases, it may be desirable to run RPU applications from the TCM. For example, when the APU is not running, the RPU may run from the TCM so that the DDR can be powered down or put into retention mode to save power.Steps to modify code memory

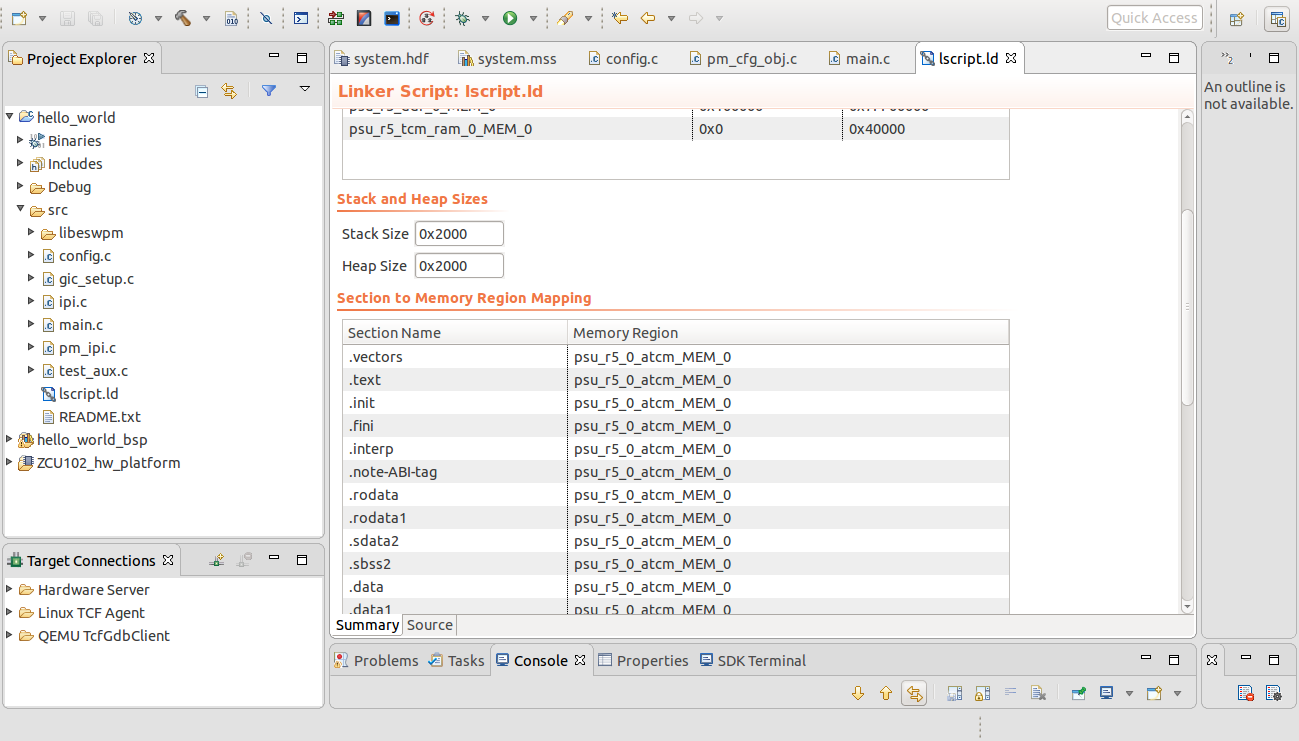

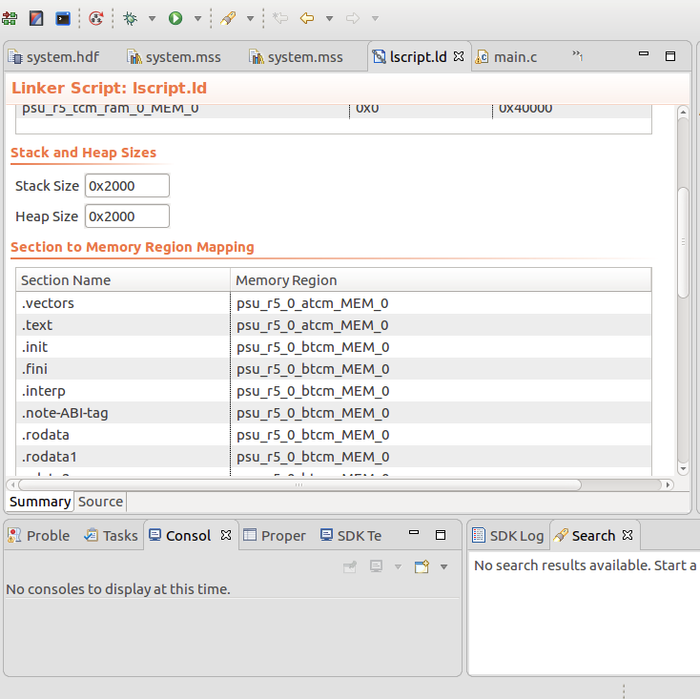

- Open lscript.ld file.

- Navigate to "Section to Memory Region Mapping" and select "psu_r5_0_atcm_MEM_0" memory region for all sections as shown below.

(Default HDF has split mode, So RPU will run in split mode. If RPU running in split mode than user has to select "psu_r5_0_atcm_MEM_0" or "psu_r5_0_btcm_MEM_0". If RPU running in lock step mode than user has to select "psu_r5_tcm_ram_0_MEM_0".) - If RPU is running in split mode, it may happen that application doesn't fit into default memory region. For that user may need to divide the sections for ATCM and BTCM memory regions in lscript.ld file. For more information please see Table 4-5: TCM Address Map in TRM. When running in split mode, each R5 processor has 64KB ATCM and 64KB BTCM. So user has to divide sections across ATCM and BTCM as per below snapshot (vectors and text sections are in ATCM and other sections are in BTCM)

- Save lscript.ld file and clean build the project.

Note: To run this example on board, FSBL and PMU needs to be run along with application elf.

© Copyright 2019 - 2022 Xilinx Inc. Privacy Policy